High Speed and Area Efficient Scalable N-bit Digital Comparator

Main Article Content

Abstract

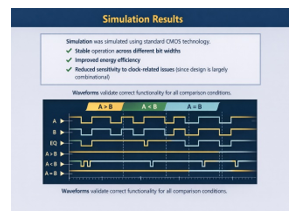

Digital comparators are fundamental components in modern digital systems, playing a crucial role in applications such as arithmetic operations, digital signal processing, pattern recognition, and data compression. Conventional comparator designs often suffer from limitations including high power consumption, increased delay, large area overhead, and sensitivity to clock-related issues. This paper proposes a scalable N-bit digital comparator that optimizes speed, power, and area using a novel Exclusive-OR–NOR (EX-OR-NOR) cell. The proposed architecture minimizes redundant computations and reduces transistor count, thereby improving overall efficiency. Simulation results demonstrate enhanced performance compared to existing comparator designs across operand sizes ranging from 4-bit to 64-bit.

Article Details

This work is licensed under a Creative Commons Attribution-NoDerivatives 4.0 International License.